Логические основы компьютера

Базовые логические элементы - дискретное устройство, которое преобразует последовательность двоичных сигналов и выдает значение одной из функций алгебры логики (логической операции), называется логическим элементом.

Дешифратор

— комбинационная схема, преобразующая n-разрядный двоичный, троичный или k-ичный код в  -ичный одноединичный код, где

-ичный одноединичный код, где  — основание системы счисления. Логический сигнал активен на том выходе, порядковый номер которого соответствует двоичному, троичному или k-ичному коду.

— основание системы счисления. Логический сигнал активен на том выходе, порядковый номер которого соответствует двоичному, троичному или k-ичному коду.

Дешифраторы являются устройствами, выполняющими двоичные, троичные или k-ичные логические функции (операции). Устройство, преобразующее входной двоичный код в сигнал на одном из выходов, называется дешифратором.

-ичный одноединичный код, где

-ичный одноединичный код, где  — основание системы счисления. Логический сигнал активен на том выходе, порядковый номер которого соответствует двоичному, троичному или k-ичному коду.

— основание системы счисления. Логический сигнал активен на том выходе, порядковый номер которого соответствует двоичному, троичному или k-ичному коду.Дешифраторы являются устройствами, выполняющими двоичные, троичные или k-ичные логические функции (операции). Устройство, преобразующее входной двоичный код в сигнал на одном из выходов, называется дешифратором.

Схема:

Назначение дешифратора:

Дешифраторы в компьютере используют, когда нужно обращаться к различным

цифровым устройствам, и при этом номер устройства – его адрес – представлен

двоичным кодом. Главное назначение дешифратора – выбор одного из устройств, номер которого приходит на вход дешифратора. В качестве таких выбираемых устройств часто выступают различные цифровые микросхемы, имеющие вход выбора кристалла

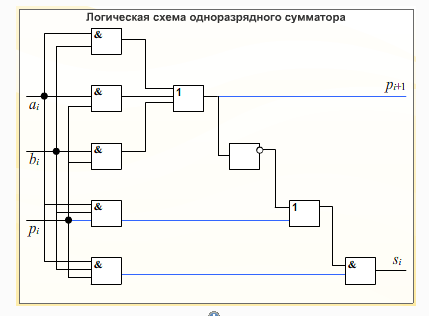

Сумматор

- устройство, преобразующее информационные сигналы (аналоговые или цифровые) в сигнал, эквивалентный сумме этих сигналов. Электронная логическая схема, которая выполняет суммирование

двоичных кодов, называется сумматором

Схема:

Назначение сумматора:

Осуществляет арифметическое суммирование n-разрядных двоичных чисел А и В. Правила сложения двух одноразрядных двоичных чисел. Сумматор, предназначенный для сложения многоразрядных двоичных чисел, представляет собой комбинацию одноразрядных сумматоров, с рассмотрения которых мы и начнём.

Триггер

- логический элемент, способный хранить один разряд двоичного числа, называется

триггером.

Для запоминания 1 байта информации необходимо 8 триггеров, для 1 Кбайта – 8 *

1024 = 8192 триггера. Оперативная память современных ЭВМ содержит миллионы

триггеров.

RS-триггер устроен следующим образом: он имеет два входа R (reset) и S (set) и два выхода Q и /%D0%9E%D0%B1%D1%80%D0%B0%D0%B7%D0%BE%D0%B2%D0%B0%D1%82%D0%B5%D0%BB%D1%8C%D0%BD%D1%8B%D0%B5%20%D0%BA%D0%BE%D0%BC%D0%BF%D0%BB%D0%B5%D0%BA%D1%81%D1%8B/%D0%98%D0%BD%D1%84%D0%BE%D1%80%D0%BC%D0%B0%D1%82%D0%B8%D0%BA%D0%B0,%2010%20%D0%BA%D0%BB/E4HOME_INFORM_10/data/res/DL_RES_DDCC9F82-2962-41A3-BC9B-C8467D8790BD/Images/1.png) . Если на выходе Q имеет

высокое напряжение, то считается, что RS-триггер хранит единицу, если

низкое, то он хранит ноль. Для выхода Q все происходит

наоборот.

. Если на выходе Q имеет

высокое напряжение, то считается, что RS-триггер хранит единицу, если

низкое, то он хранит ноль. Для выхода Q все происходит

наоборот.Если на вход R подается единица, то триггер устанавливается в состояние «0».

Если на вход S подается единица, то триггер устанавливается в состояние «1».

Если R = S = 0, то триггер сохраняет предыдущее состояние.

Состояние R = S = 1 недопустимо.

Запишем эти правила работы триггера в виде таблицы истинности для выхода Qt+1, где входами являются Rt, St и Qt. При этом Qt - текущее состояние триггера на момент времени t, а Qt+1 – состояние, в которое перейдет триггер в момент времени t + 1, обработав поступившие сигналы.

Схема:

Назначение триггера:

Триггер - устройство, предназначенное для хранения значения одной логической переменной (или значения одноразрядного двоичного числа, при хранении многоразрядных двоичных чисел для запоминания значения каждого разряда числа используется отдельный триггер). В соответствии с этим триггер имеет два состояния: одно из них обозначается как состояние лог. 0, другое - состояние лог. Воздействуя на входы триггера, его устанавливают в нужное состояние.

Триггер - устройство, предназначенное для хранения значения одной логической переменной (или значения одноразрядного двоичного числа, при хранении многоразрядных двоичных чисел для запоминания значения каждого разряда числа используется отдельный триггер). В соответствии с этим триггер имеет два состояния: одно из них обозначается как состояние лог. 0, другое - состояние лог. Воздействуя на входы триггера, его устанавливают в нужное состояние.

Комментариев нет:

Отправить комментарий